在万众瞩目的中国芯片产业崛起之路上,我们关注光刻机的精度、材料的纯度,却容易忽略一个隐匿于微观世界、威力却足以摧毁巨大投入的“隐形杀手”——静电放电(ESD)。对于内部结构已精细至纳米级的现代芯片而言,一次人体几乎无法感知的静电释放,就可能让数百亿个晶体管中的一部分瞬间失效。POUSTO将分点深入论述,为何静电防护是芯片制造不可逾越的安全底线。

极致的精密,带来极致的脆弱

一颗采用先进制程的芯片,其内部可以集成超过数百亿个晶体管,这些晶体管之间的连接线路宽度仅相当于人类发丝直径的万分之一。这种极致的精密化,是芯片实现强大算力的基础,但也使其物理强度变得异常脆弱。当带有静电荷的物体(如人体、工具)靠近或接触芯片时,所形成的静电电场强度可能高达每厘米数万伏,足以直接击穿这些纳米级的氧化层或金属线路,造成永久性的物理损伤。可以说,芯片的性能越强大,其对静电的敏感度就越高。

难以感知的能量,造成不可逆的损伤

静电的威胁在于其隐蔽性。人体通常需要感受到3000伏以上的静电放电,而许多精密芯片所能承受的静电电压阈值却低于100伏,甚至仅为10伏。这意味着,操作员在毫无察觉的情况下,其身体所携带的静电就可能已经远超芯片的承受极限。这种放电过程可能在纳秒内完成,能量瞬间注入芯片内部,导致金属熔融、氧化层击穿或电路短路。这种损伤是微观且不可逆的,一旦发生,芯片即告报废。

隐性与显性损伤:更致命的潜在威胁

静电放电造成的后果并非总是立即显现,这使其危害性倍增。它主要分为两种类型:

显性损伤(Catastrophic Failure): 即芯片被彻底损坏,功能完全丧失。这类问题能在生产测试环节中被发现,虽然导致废品,直接造成经济损失,但至少避免了有缺陷的产品流入市场。

隐性损伤(Latent Defect): 这是更具破坏性的情况。静电放电可能只对芯片造成轻微损伤,使其性能参数“带伤工作”,在初期测试中一切正常。然而,这种潜在的伤害会削弱芯片的寿命和稳定性,在产品交付给终端客户,经过数周或数月的使用后,问题才突然爆发,导致系统故障。隐性损伤不仅带来巨大的售后维修成本和品牌信誉损失,其追溯和定位也极其困难,危害深远。

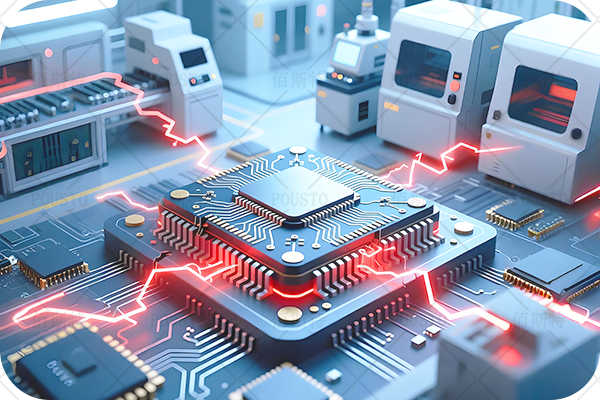

全流程的潜伏风险

静电威胁贯穿于芯片的整个生命周期——从硅片制造、封装测试、到板卡装配、直至整机生产。任何一个环节的防护疏漏,都可能导致前功尽弃。在干燥环境中移动、摩擦、包装、搬运等任何动作都可能产生静电,使得芯片在到达最终用户手中之前,始终暴露在ESD风险之下。因此,静电防护不是一个点的问题,而是一个需要全程覆盖、系统管理的面的问题。

综上所述,静电对于芯片产业而言,绝非可以掉以轻心的普通现象,而是一个必须用系统工程去应对的“头号公敌”。 其威胁源于芯片自身纳米级结构的脆弱性、静电释放的隐蔽性、以及损伤类型的潜在性和危害的全程性。在芯片技术不断向更小纳米节点迈进的今天,对静电的管控能力,直接关系到产品的良率、可靠性和企业的核心竞争力。树立对静电“零容忍”的深刻认知,是构建高标准芯片制造环境的第一步,也是守护每一颗“中国芯”成功诞生的首要前提。 上海佰斯特电子工程有限公司深知于此,致力于为行业提供从意识到装备的全方位防静电解决方案,共同筑牢这道至关重要的安全防线。

本文由上海佰斯特电子工程有限公司原创发布,转载请注明出处。如果您正在规划或升级您的芯片半导体实验室,欢迎联系我们的专家团队,为您提供免费的咨询与规划建议!

上海佰斯特电子工程有限公司:http://www.pousto.com.cn

文章出处:http://www.pousto.com.cn/xinwen/xinpianbandaoti/namijideweixieweishenme/

标题:纳米级的威胁:为什么静电是芯片制造的“隐形杀手”?_佰斯特POUSTO

地址:http://www.water-quality.cn/xwzx/37582.html